# 2 CHANNEL AUTO-BIDIRECTIONAL MULTI-VOLTAGE LEVEL TRANSLATOR FOR OPEN-DRAIN APPLICATION

#### ■ DESCRIPTION

The UTC **ULSF0102** family supports up to 100MHz up translation and greater than 100MHz down translation at≤30pF cap load and up to 40MHz up/down translation at 50pF cap load which allows the UTC **ULSF0102** family to support more consumer or telecom interfaces (MDIO or SDIO). The UTC **ULSF0102** family has bidirectional voltage translation without the need for DIR pin which minimizes system effort (for PM Bus, I²C, or SM Bus).

The UTC **ULSF0102** family supports 5V tolerance on I/O port which makes it compatible with TTL levels in industrial and telecom applications. The UTC **ULSF0102** family is able to setup different voltage translation levels on each channel which makes it very flexible.

#### ■ FEATURES

- \* Provides bidirectional voltage translation with no direction pin

- \* Supports up to 100MHz up translation and greater than 100MHz down translation at ≤ 30pF cap load and up to 40MHz up/down translation at 50pF cap load.

- \* Allow bidirectional voltage level translation between

- 0.95V ↔ 1.8/2.5/3.3/5V

- 1.2V↔1.8/2.5/3.3/5V

- $-1.8V \leftrightarrow 2.5/3.3/5V$

- 2.5V ↔ 3.3/5V

- $-3.3V \leftrightarrow 5V$

- \* Low standby current

- \* 5V tolerance I/O port to support TTL

- \* Low Ron provides less signal distortion

- \* High-Impedance I/O pins for EN=Low

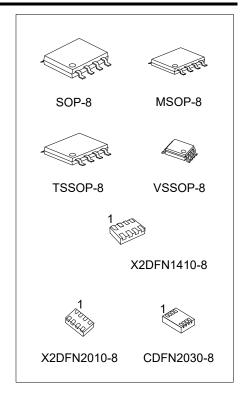

## ORDERING INFORMATION

| Ordering               | Number                 | Dealters                   | Dealine   |

|------------------------|------------------------|----------------------------|-----------|

| Lead Free              | Halogen Free           | Package                    | Packing   |

| ULSF0102L-S08-R        | ULSF0102G-S08-R        | SOP-8                      | Tape Reel |

| ULSF0102L-SM1-R        | ULSF0102G-SM1-R        | MSOP-8                     | Tape Reel |

| ULSF0102L-P08-R        | ULSF0102G-P08-R        | TSSOP-8                    | Tape Reel |

| ULSF0102L-V08-R        | ULSF0102G-V08-R        | VSSOP-8                    | Tape Reel |

| ULSF0102L-CK08-2030-R  | ULSF0102G-CK08-2030-R  | 02G-CK08-2030-R CDFN2030-8 |           |

| ULSF0102AL-SM1-R       | ULSF0102AG-SM1-R       | MSOP-8                     | Tape Reel |

| ULSF0102AL-V08-R       | ULSF0102AG-V08-R       | VSSOP-8                    | Tape Reel |

| ULSF0102AL-CK08-2030-R | ULSF0102AG-CK08-2030-R | CDFN2030-8                 | Tape Reel |

| ULSF0102AL-KAD-R       | ULSF0102AG-KAD-R       | X2DFN1410-8                | Tape Reel |

| ULSF0102AL-KAY-R       | ULSF0102AG-KAY-R       | X2DFN2010-8                | Tape Reel |

# MARKING

| PACKAGE     | ULSF0102                                                                | ULSF0102A                                                            |

|-------------|-------------------------------------------------------------------------|----------------------------------------------------------------------|

| SOP-8       | B 7 6 5  UTC OCCUPATION Date Code L: Lead Free C: Halogen Free Lot Code | -                                                                    |

| MSOP-8      | B 7 6 5  UTC DDDD  ULSF0102D  G: Halogen Free  Lot Code                 | B 7 6 5  UTC COCC L: Lead Free L: Lead Free G: Halogen Free Lot Code |

| TSSOP-8     | ULSF0102 6 L: Lead Free  G: Halogen Free  Lot Code                      | -                                                                    |

| VSSOP-8     | Date Code  L: Lead Free  G: Halogen Free  Lot Code                      | Date Code  U2A L: Lead Free  G: Halogen Free  Lot Code               |

| CDFN2030-8  | ULSF<br>0102<br>•□□□□<br>→ Date Code                                    | ULSF<br>0102A<br>•□□□□<br>→ Date Code                                |

| X2DFN1410-8 | -                                                                       | U2A<br>●                                                             |

| X2DFN2010-8 | -                                                                       | U2A                                                                  |

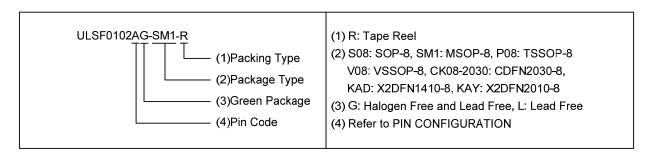

## ■ PIN CONFIGURATION

# ■ PIN DESCRIPTION

| PIN NO.  |           | DININIANE    | DESCRIPTION                                                                     |  |  |

|----------|-----------|--------------|---------------------------------------------------------------------------------|--|--|

| ULSF0102 | ULSF0102A | PIN NAME     | DESCRIPTION                                                                     |  |  |

| 4        | 1         | GND          | Ground                                                                          |  |  |

| 3        | 2         | $V_{REF\_A}$ | Reference supply voltage                                                        |  |  |

| 1, 2     | 3, 4      | An           | Data port                                                                       |  |  |

| 7 ,8     | 5, 6      | Bn           | Data port                                                                       |  |  |

| 6        | 7         | $V_{REF\_B}$ | Reference supply voltage                                                        |  |  |

| 5        | 8         | EN           | Switch enable input; connect to $V_{REF\_B}$ and pull-up through a high R(200K) |  |  |

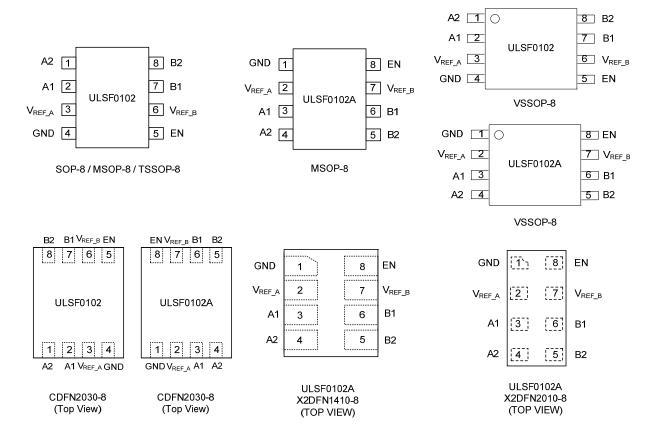

# ■ BLOCK DIAGRAM

## ■ FUNCTION TABLE

| INPUT EN PIN | FUNCTION |  |  |

|--------------|----------|--|--|

| Н            | An = Bn  |  |  |

| L            | H-Z      |  |  |

Note: EN is controlled by V<sub>REF\_B</sub> logic levels.

## ■ ABSOLUTE MAXIMUM RATING (T<sub>A</sub>=25°C, unless otherwise specified) (Note)

| PARAMETER                  | SYMBOL           | CONDITIONS          | RATINGS    | UNIT |

|----------------------------|------------------|---------------------|------------|------|

| Input Voltage              | V <sub>IN</sub>  |                     | -0.5 ~ 7   | V    |

| Input/Output Voltage       | V <sub>I/o</sub> |                     | -0.5 ~ 7   | V    |

| Continuous Channel Current |                  |                     | 128        | mA   |

| Input Clamp Current        | I <sub>IK</sub>  | V <sub>IN</sub> <0V | -50        | mA   |

| Storage Temperature Range  | T <sub>STG</sub> |                     | -65 ~ +150 | °C   |

Note: Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied.

## ■ RECOMMENDED OPERATING CONDITIONS

| PARAMETER               | SYMBOL                  | CONDITIONS | MIN | TYP | MAX  | UNIT |

|-------------------------|-------------------------|------------|-----|-----|------|------|

| Input/Output Voltage    | V <sub>I/O</sub>        |            | 0   |     | 5.5  | ٧    |

| Reference Voltage       | V <sub>REF_A/B/EN</sub> |            | 0   |     | 5.5  | ٧    |

| Pass Transistor Current | IPASS                   |            |     |     | 64   | mΑ   |

| Operating Temperature   | TA                      |            | -40 |     | +125 | °C   |

## ■ ELECTRICAL CHARACTERISTICS (T<sub>A</sub>=25°C, unless otherwise specified)

| PARAMETER                          | SYMBOL                               | TEST COND                                                                                          | ITIONS                                                                 | MIN | TYP | MAX  | UNIT |

|------------------------------------|--------------------------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|-----|-----|------|------|

| Input Clamp Voltage                | Vıĸ                                  | I <sub>I</sub> =-18mA ,V <sub>EN</sub> =0V                                                         |                                                                        |     |     | -1.2 | V    |

| Input Leakage Current              | Іін                                  | V <sub>IN</sub> =5V, V <sub>EN</sub> =0V                                                           |                                                                        |     |     | 5    | μΑ   |

| Quiescent Supply Current           | Icc                                  | V <sub>REF_B</sub> =V <sub>EN</sub> =5.5V,<br>V <sub>REF_A</sub> =4.5V or 1V, I <sub>O</sub> =0, \ | /ı=Vcc or GND                                                          |     | 6   |      | μA   |

| Input Capacitance                  | CIN                                  | V <sub>I</sub> =3V or 0V                                                                           |                                                                        |     | 6   |      | рF   |

| Off Capacitance                    | C <sub>IO(OFF)</sub>                 | V <sub>I</sub> =3V or 0V, V <sub>EN</sub> =0                                                       |                                                                        |     |     | 6    | pF   |

| Capacitance When Switch Is Enabled | C <sub>IO(ON)</sub>                  | V <sub>I</sub> =3V or 0V, V <sub>EN</sub> =3V                                                      |                                                                        |     |     | 12.5 | pF   |

|                                    |                                      |                                                                                                    | V <sub>REF_A</sub> =3.3V,<br>V <sub>REF_B</sub> =V <sub>EN</sub> =5V   |     | 3   |      | Ω    |

|                                    |                                      | V <sub>I</sub> =0V, I <sub>O</sub> =64mA                                                           | V <sub>REF_A</sub> =1.8V,<br>V <sub>REF_B</sub> =V <sub>EN</sub> =5V   |     | 4   |      | Ω    |

|                                    |                                      |                                                                                                    | V <sub>REF_A</sub> =1.0V,<br>V <sub>REF_B</sub> =V <sub>EN</sub> =5V   |     | 7   |      | Ω    |

|                                    |                                      | V <sub>I</sub> =0V, I <sub>O</sub> =32mA                                                           | V <sub>REF_A</sub> =1.8V,<br>V <sub>REF_B</sub> =V <sub>EN</sub> =5V   |     | 4   |      | Ω    |

| Switch On Resistance<br>(Note 2)   | Ron                                  |                                                                                                    | $V_{REF\_A}$ =2.5V,<br>$V_{REF\_B}$ = $V_{EN}$ =5V                     |     | 3   |      | Ω    |

|                                    |                                      | V <sub>I</sub> =1.8V, I <sub>O</sub> =15mA                                                         | $V_{REF\_A}$ =3.3V,<br>$V_{REF\_B}$ = $V_{EN}$ =5V                     |     | 6   |      | Ω    |

|                                    |                                      | V <sub>i</sub> =1V, I <sub>0</sub> =10mA                                                           |                                                                        |     | 7   |      | Ω    |

|                                    | V <sub>I</sub> =0V, I <sub>O</sub> = | V <sub>I</sub> =0V, I <sub>O</sub> =10mA                                                           | $V_{REF\_A}$ =1.0V,<br>$V_{REF\_B}$ = $V_{EN}$ =3.3V                   |     | 5   |      | Ω    |

|                                    |                                      | V <sub>I</sub> =0V, I <sub>O</sub> =10mA                                                           | V <sub>REF_A</sub> =1.0V,<br>V <sub>REF_B</sub> =V <sub>EN</sub> =1.8V |     | 6   |      | Ω    |

Notes: 1. All typical values are at T<sub>A</sub>=25°C.

2. Measured by the voltage drop between the A and B terminals at the indicated current through the switch. On-state resistance is determined by the lowest voltage of the two (A or B) terminals.

ULSF0102

# ■ SWITCHING CHARACTERISTICS

| PARAMETER                                                      |       | SYMBOL           | TEST CONDITIONS                                                                                                           |                      | MIN | TYP | MAX | UNIT |

|----------------------------------------------------------------|-------|------------------|---------------------------------------------------------------------------------------------------------------------------|----------------------|-----|-----|-----|------|

|                                                                |       |                  | V <sub>REF_A</sub> =2.3V, V <sub>REF_B</sub> =3.3V,                                                                       | C <sub>L</sub> =50pF |     | 1.7 |     | ns   |

| Propagation Delay<br>From Input (A or B) to<br>Output (B or A) | Down  |                  | V <sub>IH</sub> =3.3V, V <sub>IL</sub> =0, V <sub>M</sub> =1.15V                                                          | C <sub>L</sub> =15pF |     | 1.4 |     | ns   |

|                                                                |       |                  | $V_{REF\_A}$ =1.5V, $V_{REF\_B}$ =2.5V,                                                                                   | C <sub>L</sub> =50pF |     | 1.6 |     | ns   |

|                                                                |       |                  | $V_{IH}=2.5V, V_{IL}=0, V_{M}=0.75V$                                                                                      | C <sub>L</sub> =15pF |     | 1.5 |     | ns   |

|                                                                |       | t <sub>PLH</sub> | V <sub>REF_A</sub> =2.3V, V <sub>REF_B</sub> =3.3V,<br>V <sub>IH</sub> =2.3V, V <sub>IL</sub> =0, V <sub>T</sub> =3.3V,   | C <sub>L</sub> =50pF |     | 1.7 |     | ns   |

|                                                                | Lla   |                  | $V_M=1.15V, R_L=300\Omega$                                                                                                | C <sub>L</sub> =15pF |     | 1.6 |     | ns   |

|                                                                | Up    |                  | $V_{REF\_A}$ =1.5V, $V_{REF\_B}$ =2.5V, $V_{IH}$ =2.5V, $V_{IL}$ =0, $V_{T}$ =2.5V, $V_{M}$ =0.75V, $R_{L}$ =300 $\Omega$ | C <sub>L</sub> =50pF |     | 2   |     | ns   |

|                                                                |       |                  |                                                                                                                           | C <sub>L</sub> =15pF |     | 1.9 |     | ns   |

|                                                                | Dours |                  | V <sub>REF_A</sub> =2.3V, V <sub>REF_B</sub> =3.3V,                                                                       | C <sub>L</sub> =50pF |     | 7.7 |     | ns   |

|                                                                |       |                  | V <sub>IH</sub> =3.3V, V <sub>IL</sub> =0, V <sub>M</sub> =1.15V                                                          | C <sub>L</sub> =15pF |     | 4.6 |     | ns   |

|                                                                | Down  |                  | V <sub>REF_A</sub> =1.5V, V <sub>REF_B</sub> =2.5V,                                                                       | C <sub>L</sub> =50pF |     | 5.2 |     | ns   |

| Propagation Dolay                                              |       |                  | V <sub>IH</sub> =2.5V, V <sub>IL</sub> =0, V <sub>M</sub> =0.75V                                                          | C <sub>L</sub> =15pF |     | 5.1 |     | ns   |

| Propagation Delay<br>From Input (A or B) to<br>Output (B or A) |       | t <sub>PHL</sub> | V <sub>REF_A</sub> =2.3V, V <sub>REF_B</sub> =3.3V,<br>V <sub>IH</sub> =2.3V, V <sub>IL</sub> =0, V <sub>T</sub> =3.3V,   | C <sub>L</sub> =50pF |     | 6.8 |     | ns   |

|                                                                | 1.1   |                  | $V_{M}$ =1.15V, $R_{L}$ =300 $\Omega$                                                                                     | C <sub>L</sub> =15pF |     | 6.5 |     | ns   |

|                                                                | Up    |                  | V <sub>REF_A</sub> =1.5V, V <sub>REF_B</sub> =2.5V,<br>V <sub>IH</sub> =2.5V, V <sub>IL</sub> =0, V <sub>T</sub> =2.5V,   | C <sub>L</sub> =50pF |     | 5.3 |     | ns   |

|                                                                |       |                  | V <sub>M</sub> =0.75V, R <sub>L</sub> =300Ω                                                                               | C <sub>L</sub> =15pF |     | 5.2 |     | ns   |

**CMOS IC**

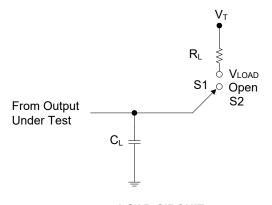

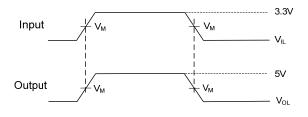

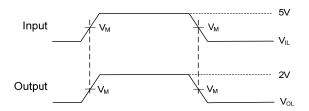

# ■ TEST CIRCUIT AND WAVEFORMS

| USAGE            | SWITCH |

|------------------|--------|

| Translating Up   | S1     |

| Translating Down | S2     |

LOAD CIRCUIT

TRANSLATING UP

TRANSLATING DOWN

Notes: 1.  $C_L$  includes probe and jig capacitance.

- 2. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $Z_0$  = 50 $\Omega$ ,  $t_r \leq$  2 ns,  $t_f \leq$  2 ns.

- 3. The outputs are measured one at a time, with one transition per measurement.

#### DEVICE FUNCTIONAL MODES

For each channel (n), when either the An or Bn port is LOW, the switch provides a low impedance path between the An and Bn ports; the corresponding Bn or An port will be pulled LOW. The low R<sub>ON</sub> of the switch allows connections to be made with minimal propagation delay and signal distortion.

When the signal is being driven from A to B and the An port is HIGH, the switch will be OFF and the Bn port will then driven to a voltage higher than  $V_{REF\_A}$  by the pullup resistor that is connected to the pull-up supply voltage ( $V_{PU}\#$ ). This functionality allows seamless translation between higher and lower voltages selected by the user, without the need for directional control.

Refer to Function table for a summary of device operation. For additional details on the functional operation of the UTC **ULSF0102** family of devices, see the Down Translation with the UTC **ULSF0102** Family and Up Translation with the UTC **ULSF0102** Family videos.

Signal Direction (Note)

A TO B (Up Translation)

A TO B (Up Translation)

A=HIGH

Input State

Switch State

ON

(Low Impedance)

OFF

(High Impedance)

B-side voltage is pulled low through the switch to the A-side voltage

B-side voltage is clamped at V<sub>REF\_A</sub> and then pulled up to the V<sub>PU</sub> # supply voltage

Table 1. Device Functionality

Note: The downstream channel should not be actively driven through a low impedance driver, or else there may be bus contention.

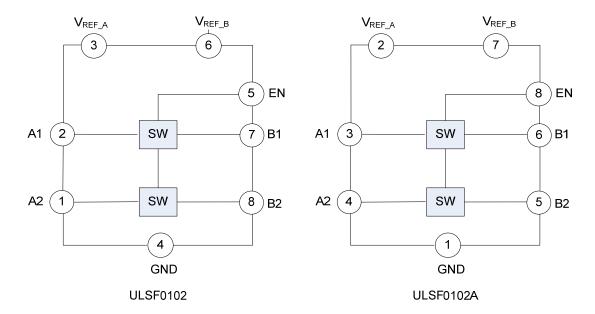

#### ■ TYPICAL APPLICATIONS

The UTC **ULSF0102** family has an EN input that is used to disable the device by setting EN LOW, placing all I/Os in the high-impedance state. Since the UTC **ULSF0102** family of devices are switch-type voltage translators, the power consumption is very low. UTC recommends always enabling the UTC **ULSF0102** family for bidirectional applications (I<sup>2</sup>C, SMBus, PMBus, or MDIO).

| PARAMETER                  | SYMBOL             | TEST CONDITIONS | MIN                     | TYP | MAX                | UNIT |

|----------------------------|--------------------|-----------------|-------------------------|-----|--------------------|------|

| Reference Voltage A (Note) | V <sub>REF_A</sub> |                 | 0.95                    |     | 4.5                | V    |

| Reference Voltage B        | V <sub>REF_B</sub> |                 | V <sub>REF_A</sub> +0.8 |     | 5.5                | V    |

| Input Voltage on EN Pin    | V <sub>I(EN)</sub> |                 | V <sub>REF_A</sub> +0.8 |     | 5.5                | ٧    |

| Pull-Up Supply Voltage     | V <sub>PU</sub>    |                 | 0                       |     | V <sub>REF_B</sub> | V    |

Table 2. Application Operating Condition

Note: V<sub>REF\_A</sub> is required to be the lowest voltage level across all inputs and outputs.

The 200 k $\Omega$ , pull-up resistor is required to allow  $V_{REF\_B}$  to regulate the EN input and properly bias the device for translation. A filter capacitor on  $V_{REF\_B}$  is recommended. Also  $V_{REF\_B}$  and  $V_{I(EN)}$  are recommended to be 1.0V higher than  $V_{REF\_B}$  for best signal integrity.

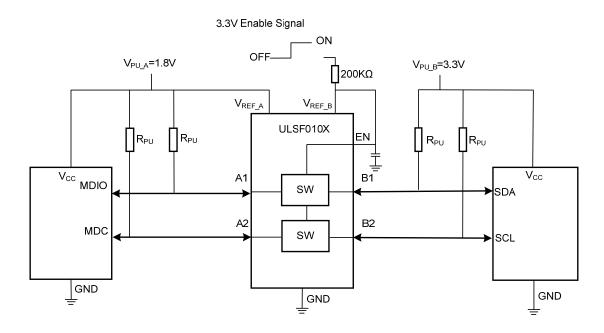

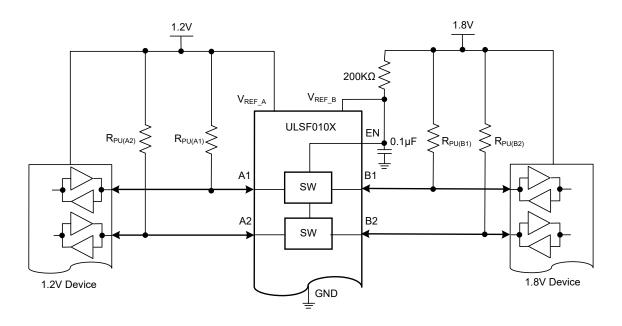

### ■ TYPICAL APPLICATIONS (Cont.)

#### **Bidirectional Translation**

For the bidirectional translation configuration (higher voltage to lower voltage or lower voltage to higher voltage), the EN input must be connected to  $V_{REF\_B}$  and both pins must be pulled up to the HIGH side  $V_{PU}$  through a pull-up resistor (typically 200 k $\Omega$ ). This allows  $V_{REF\_B}$  to regulate the EN input and bias the channels for proper translation. A filter capacitor on  $V_{REF\_B}$  is recommended for a stable supply at the device. The controller output driver can be open-drain (pull-up resistors may be required) and the peripheral device output can be push-pull or open-drain (pull-up resistors are required to pull the Bn outputs to  $V_{PU}$ ).

If either output is push-pull, data must be unidirectional or the outputs must be tri-state and be controlled by some direction-control mechanism to prevent HIGH-to-LOW bus contention in either

direction. If both outputs are open-drain, no direction control is needed.

When  $V_{REF\_B}$  is connected through a 200k $\Omega$  resistor to a 3.3V  $V_{PU}$  power supply and  $V_{REF\_A}$  is set 1.8 V, as shown in Figure 1, the A1 and A2 channels have a maximum output voltage equal to  $V_{REF\_A}$ , and the B1 and B2 channels have has a maximum output voltage equal to  $V_{PU}$ .

## **Pull-up Resistor Sizing**

The pull-up resistor value needs to limit the current through the pass transistor when it is in the ON state to about 15mA. This ensures a voltage drop of 260mV to 350mV to have a valid LOW signal on the downstream channel. If the current through the pass transistor is higher than 15mA, the voltage drop is also higher in the ON state. To set the current through each pass transistor at 15mA, calculate the pull-up resistor value using the following equation:

$$R_{PU} = (V_{PU} - 0.35V) / 0.015A (1)$$

Table 3 summarizes resistor values, reference voltages, and currents at 15mA, 10mA, and 3mA. The resistor value shown in the +10% column (or a larger value) should be used to ensure that the voltage drop across the transistor is 350 mV or less. The external driver must be able to sink the total current from the resistors on both sides of the UTC **ULSF0102** family device at 0.175V, although the 15mA applies only to current flowing through the UTC **ULSF0102** family device.

| \/                             | 15mA              |                  | 10mA       |                  | 3mA        |                  |  |

|--------------------------------|-------------------|------------------|------------|------------------|------------|------------------|--|

| V <sub>DPU</sub><br>(Note1, 2) | $NOMINAL(\Omega)$ | +10%(Ω) (Note 3) | NOMINAL(Ω) | +10%(Ω) (Note 3) | NOMINAL(Ω) | +10%(Ω) (Note 3) |  |

| 5V                             | 310               | 341              | 465        | 512              | 1550       | 1705             |  |

| 3.3V                           | 197               | 217              | 295        | 325              | 983        | 1082             |  |

| 2.5V                           | 143               | 158              | 215        | 237              | 717        | 788              |  |

| 1.8V                           | 97                | 106              | 145        | 160              | 483        | 532              |  |

| 1.5V                           | 77                | 85               | 115        | 127              | 383        | 422              |  |

| 1.2V                           | 57                | 63               | 85         | 94               | 283        | 312              |  |

Table 3. Pull-up Resistor Values

Notes: 1. Calculated for V<sub>OL</sub>=0.35V.

- 2. Assumes output driver  $V_{\text{OL}}$ =0.175V at stated current.

- 3. +10% to compensate for V<sub>DD</sub> range and resistor tolerance.

## ■ TYPICAL APPLICATION CIRCUIT

Figure 1. Typical Application Circuit for Open-Drain Translation (MDIO shown as an example)

Figure 2. 1.2 to 1.8V Level Translation with ULSF010X

UTC assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all UTC products described or contained herein. UTC products are not designed for use in life support appliances, devices or systems where malfunction of these products can be reasonably expected to result in personal injury. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. UTC reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.